Morizio, J., Hoke, M., Kocak, T., & Geddie, C. (2000). SNDR sensitivity analysis for cascaded ΣΔ modulators. In *ÍEEE International* Symposium on Circuits and Systems. Emerging Technologies for the 21st Century, Geneva (Vol. 3, pp. 765 - 762). Institute of Electrical and Electronics Engineers (IEEE). https://doi.org/10.1109/ISCAS.2000.856172

Peer reviewed version

Link to published version (if available): 10.1109/ISCAS.2000.856172

Link to publication record on the Bristol Research Portal PDF-document

# University of Bristol – Bristol Research Portal General rights

This document is made available in accordance with publisher policies. Please cite only the published version using the reference above. Full terms of use are available: http://www.bristol.ac.uk/red/research-policy/pure/user-guides/brp-terms/

### SNDR Sensitivity Analysis for Cascaded ΣΔ Modulators

James Morizio, Michael Hoke, Taskin Kocak, Clark Geddie, Chris Hughes, John Perry, Srinadh Madhavapeddi, Michael Hood, Ward Huffman

Mitsubishi Electronics America - Electronic Device Group, Durham, NC 27704

Takashi Okuda, Hiroshi Noda, Yasuo Morimoto, Toshio Kumamoto, Masahiko Ishiwaki, Harufusa Kondoh, Masao Nakaya, Takahiro Miki

Mitsubishi Electric Corporation - System LSI Division, Hyogo 664-8641 Japan

#### Abstract

Cascade, single and multi-bit,  $\Sigma\Delta$  architectures provide stable, high order quantization noise shaping used in high resolution A/D conversion. One major disadvantage of cascaded  $\Sigma\Delta$  topologies is the extreme SNDR sensitivity to gain mismatch between the analog modulator and the digital error correction logic. This paper will investigate this SNDR sensitivity phenomenon for a 6th order, I-bit quantizer and 4th order, 5-bit quantizer cascaded  $\Sigma\Delta$  A/D system. Circuit parameters of the switched capacitor integrator such as amplifier open loop gain, integrator gain, and amplifier offsets and layout parasitics will be characterized.

### 1. Introduction

Cascaded  $\Sigma\Delta$  modulators achieve stable, higher order noise shaping with reduced oversampling rates[1,2]. These modulator topologies consist of a series of lower order modulators, each with its own quantizer. The quantizer input of each loop is fed to the next stage, where the quantization noise of the previous stage is corrected. At the final output, only the quantization error of the last stage exist, thus resulting in high order noise shaping. An digital error correction stage combines all quantizer outputs to produce the intended, oversampled digitized output. Integrator gain matching requirements between the error correction and cascaded modulators become a problem. In practical implementations, increasing the resolution of the multi-bit quantizer reduces the second-stage quantization error and increases the sensitivity to uncancelled quantization error from the first stage [5]. A cascaded, 4th order modulator with 5-bit quantization and a 6th order, 1-bit quantizer is described in sections 1.1 and 1.2 respectively.

#### 1.1 4th order 5-bit Analog Modulator

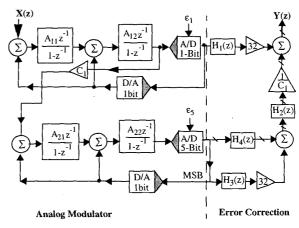

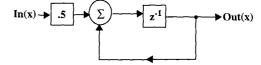

The 4th order modulator shown in Figure 1 consists of two cascaded second order stages which include a 1-bit and 5-bit quantizer respectively. This will result in 4th order noise shaping with 5 bit quantization[3]. The error correction stage will combine the 1-bit digital output from the first stage with 5-bit and 1-bit digital outputs from the second stage, to yield an output comprised of the input signal plus a fourth order error term.

Figure 1: 4th Order Modulator

Transfer functions for the error correction filters of the 4th order system in Figure 1 can be given as follows:

$$H_1(z) = k(A_1A_2)z^{-2}(1-k(1-z^{-1})^2)$$

Eq: 1

$$H_2(z) = k(1-z^{-1})^2$$

Eq. 2

$$H_3(z) = 1 - k(1 - z^{-1})^2$$

Eq: 3

$$H_4(z) = k(1-z^{-1})^2$$

Eq: 4

$$k = \frac{1}{1 + (A_2 - 2)z^{-1} + (A_1 A_2 - A_2 + 1)z^{-2}}$$

Eq. 5

The overall system transfer function Y(z) is below:

$$Y(z) = k^2 \left( X(z) (A_1 A_2)^2 z^{-4} + \frac{\varepsilon_5}{C_1} (1 - z^{-1})^4 \right)$$

Eq: 6

Notice the 5-bit quantization noise error term,  $\varepsilon_5$ , with 4th order noise shaping  $(1-z^{-1})^4$ . This is the desired noise shaping required for this system transfer function. Following the error correction logic is a cascaded decimator section which includes a Sinc<sup>5</sup> filter and a 24 tap FIR filter[4].

#### 1.2 6th order 1-bit Analog Modulator

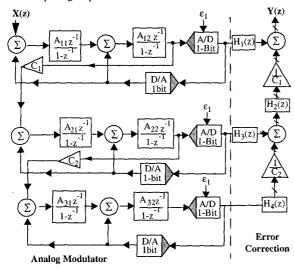

The 6th order modulator consists of three cascaded second order stages as shown in Figure 2. This cascaded topology was chosen to take advantage of both the stability provided by its lower order sections and the 6th order noise shaping of the overall system. The 1-bit digital outputs of each of the three stages are combined and digitally filtered to yield an output comprised of the input signal plus a 6th order noise error term.

Figure 2: 6th Order Modulator

The 6th order modulator structure is very similar to the 4th order structure shown in Figure 1. Likewise, the error correction filters in the 6th order system have the same transfer functions as their counterparts in the 4th order system with the exception of  $H_1(z)$  and  $H_3(z)$ , which are modified as follows:

$$H_1(z) = k^2 (A_1 A_2)^2 z^{-4} (1 - k(1 - z^{-1})^2)$$

Eq: 7

$H_3(z) = k A_1 A_2 z^{-2} (1 - k(1 - z^{-1})^2)$  Eq: 8

The 6th order system transfer function for Y(z) is below:

$$Y(z) = k^3 \left( X(z) (A_1 A_2)^3 z^{-6} + \frac{\varepsilon_1}{C_1 C_2} (1 - z^{-1})^6 \right)$$

Eq: 9

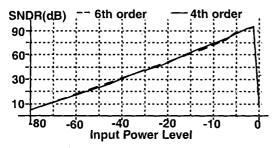

Notice the desired 6th order noise shaping term for the 1 bit A/D quantization noise error,  $\varepsilon_1$ . Following the error correction logic is a cascaded decimator section which includes a Sinc<sup>7</sup> filter and a 24 tap FIR filter. Simulated ideal SNDR plots versus input amplitude for the ADC systems are shown in Figure 3.

Figure 3: SNDR versus Amplitude Plots

## 2. Ideal Switch Capacitor Integrator

Switched capacitor  $\Sigma\Delta$  analog modulators use discrete time integrators to perform the integration of signal error required for noise shaping. The ideal integrator analysis is and linear model response is described this section[5].

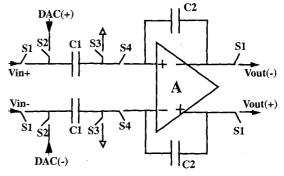

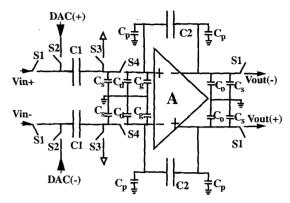

The three key circuit components of the discrete time integrators are the electrical switches, gain capacitors and the operational transconducance amplifier(OTA). An ideal switch capacitor integrator system is shown below:

Figure 4: Switch Capacitor Ideal Integrator

The linear model used in Matlab simulation is shown in Figure 5 representing the switch capacitor discrete time system.

Figure 5: Ideal Integrator Model

The integrator transfer function in Equation 1 is represent by equation 10 and is shown below:

$$H_{Ideal}(z) = \frac{z^{-1}}{2(1-z^{-1})}$$

Eq: 10

This z domain transfer function contains a pole exactly at the unit circle, simple zero at zero which is represented as a unit clock delay, and a dc gain term of a half[6].

### 3. Leaky Integrator Analysis

A discrete time integrator that contains a pole other than at the unit circle becomes an FIR filter rather than integrator. Passive parasitics around the circuit integrator and non ideal circuit parameters of the OTA also make the ideal transfer function non ideal. Hence, the name leaky integrator[7]. When we add the parasitics of wire capacitors to the common centroid layout, source

drain capacitors of the switches and input and output capacitances of the OTA, our integrator model is shown in Figure 6:

Figure 6: Switch Capacitor Leaky Integrator

Using conservation of charge derivations in the time domain, system variables gain eror ( $\alpha$ ), parasitic erors ( $\eta$ ,  $\gamma$ ), and offset error (p) can be derived as functions Cs, Cd, Cg, Cp, and Co. Also, S1 and S3 are out of phase clocks with respect to S2 and S4. These system variables for the leaky integrator are now shown below in Equations 11-14:

$$\eta = 1 + \frac{C_g + C_d}{C2(1 + A)}$$

Eq: 11

$$\gamma = \left(1 + \frac{(C1 + C_s + C_g + C_d)}{C2(1 + A)}\right)^{-1}$$

Eq: 12

$$\alpha = \frac{C1}{C2} \left( \frac{A}{1+A} \right)$$

Eq: 13

$$\rho = \frac{C1}{C2} \left( \frac{A}{1+A} \right) \left( 1 + \frac{C_s}{C1} \right)$$

Eq: 14

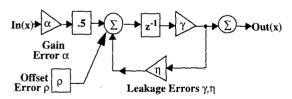

The linear model for the Leaky Integrator is shown below:

Figure 7: Leaky Integrator Parasitic Model

$$H_{Leaky}(z) = \frac{\gamma z^{-1} (\alpha + 2\rho z)}{2(1 - \gamma \eta z^{-1})}$$

Eq: 15

The  $\gamma$  and  $\eta$  feedforward and feedback parameters set the pole and zero of the switch capacitor integrator. Note  $\eta$  is > 1 and  $\gamma$  < 1. The  $\alpha$  parameter is considered the gain error of the switch capacitor integrator[8,9]. The p parameter is analogous to a filtered dc offset. If this dc offset resides in the range of the OTA, it should not create a problem with respect to SNDR, only the input range. Thus, a sensitivity analysis with respect to the p parameter is not performed. In addition, all ADC gain parameters - namely A<sub>11</sub>, through A<sub>33</sub>, C<sub>1</sub>, C<sub>2</sub> - were set to 0.5 so that a unit capacitor based centroid capacitor layout could be used. Thus, the ratio of C2/C1 = 0.5. A folded cascode integrator with

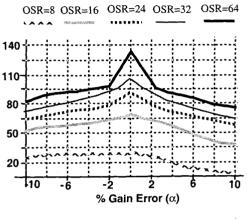

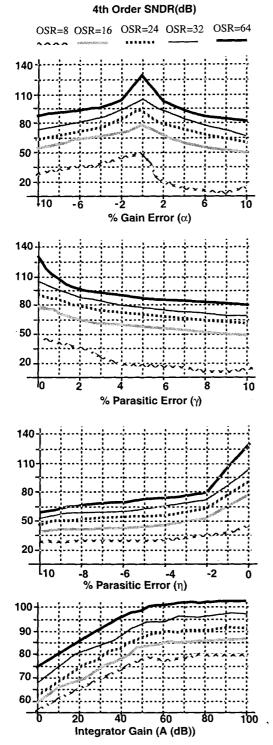

was designed, For this layout, C2 = 2.64 pF, C1 = 1.32 pF, C0 = 8pF, Cg = 3.2 pF, Cp = 0.01 pF, Cs = Cd = 0.4 pF. Thus,  $\eta = 1.00$ ,  $\gamma = 0.99$  and  $\alpha = 0.5$  and  $\rho = 0.65$ . These system parameters were simulated in Matlab for 4th and 6th order systems and results are below:

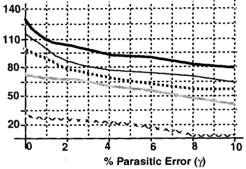

#### 6th Order SNDR(dB)

Figure 8: SNDR Sensitivity for 6th order

slew rate of 475 V/μs, Bandwidth of 1 Ghz and dc Gain of 58dHI-763

# 4. Evaluation Results

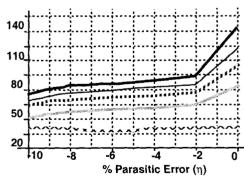

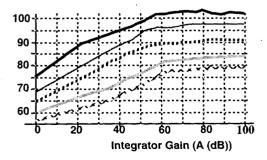

Figure 9: SNDR Sensitivity for 4th order

The table below show SNDR sensitivity with respect to system parameters for -6 dB and -12 dB attenuation in peak SNDR. Note values are entered as %.

| 6th Order, 1-Bit      | OSR     |         |         |         |         |

|-----------------------|---------|---------|---------|---------|---------|

| System Parameters     | 8       | 16      | 24      | 32      | 64      |

| % α (Gain Error)      | 3 6     | 2   4   | 1   4   | 1   4   | .5 1.5  |

| % γ (Parasitic Error) | 4 6     | 3   5   | 1.3 3   | .7 1.5  | .3   .8 |

| % η (Parasitic Error) | 5 20+   | 1   2   | .8  1.6 | .5  1   | .4   1  |

| A (OTA dc Gain)       | 1 6     | 2   8   | 2   8   | 2 9     | 4  10   |

| 4th Order, 5-Bit      | OSR     |         |         |         |         |

| System Parameters     | 8       | 16      | 24      | 32      | 64      |

| % α (Gain Error)      | .1   .4 | 1   2   | .4   1  | .3   .9 | .2 .7   |

| % γ (Parasitic Error) | .4   1  | .6   2  | 1.3 3   | 1.4 3   | .4  1   |

| % η (Parasitic Error) | .4   1  | .6   .9 | .6   .9 | .6   .8 | .2 .6   |

| A (OTA dc Gain)       | 2   7   | 2   8   | 2   8   | 2 8     | 3 9     |

Table 1. -6dB | -12dB SNDR Sensitivity

### 5. Conclusion

In this paper we investigated the SNDR sensitivity phenomenon for a 6th order, 1-bit quantizer and a 4th order, 5-bit quantizer cascaded  $\Sigma\Delta$  A/D system. Circuit parameters of the switched capacitor integrators such as amplifier open loop gain, integrator gain, and amplifier offsets and layout parasitics were quantified. Simulations data was presented and quantified to show % dependencies for that particular parameter.

### 6. References

- [1] B. Boser and B. Wooley, "The Design of Sigma-Delta Modulation Analog to Digital Converters," *IEEE Journal* of Solid State Circuits, vol. 23, No. 6, June 1988.

- [2] J. Candy, "Use of Double Integration in Sigma-delta Modulation," *IEEE Transactions on Communications*, vol. Com-33, No.3, March 1985.

- [3] J. Candy and G. Temes, "Oversampling Delta-Sigma Data Converters," IEEE Press, New York, N.Y.,1992.

- [4] A. Feldman, "High Speed, Low Power-Delta Modulators for RF Baseband Channel Applications," Ph. D. Dissertation, University of California Berkeley, June 1998.

- [5] M. Rebeschini, "Delta Sigma Data Converters: Theory, Design, and Simulation", IEEE Press, 1996, Chapter 6.

- [6] J. Morizio, "Adaptive Gain Sigma Delta Architectures", Ph.D. Dissertation, Duke University, 1995, pp 19-37.

- [7] T. Leslie and B. Singh, "An Improved Sigma-Delta Modulator Architecture," *IEEE Proceedings from ICASSP*, pp. 372-375, May 1990.

- [8] G. Temes and T. Catatepe, "Multi-bit Oversampled Sigmadelta A/D Converters with Digital Error Correction," *Electronic Letters*,vol. 24, pp. 1051 - 1052, August 1988

- [9] M. J. McNutt, S. LeMarquis and J.L. Dunkley, "Systematic Capacitance Matching Errors and Corrective Layout Procedures", *IEEE Journal of Solid-State Circuits*, vol. 29, no. 5, pp. 611-616, 1994.